# Two PLL Programmable Clock Generator with Spread Spectrum

### Features

- Two fully integrated phase-locked loops (PLLs)

- Input Frequency range:

- External crystal: 8 to 48 MHz

- External reference: 8 to 166 MHz clock

- Wide operating output frequency range

- 3 to 166 MHz

- Programmable Spread Spectrum modulation frequency range of 30 to 120 kHz with Lexmark profile

- Center Spread: ±0.125% to ±2.5%

- Down Spread: -0.25% to -5%

- Frequency select feature with option to select four different frequencies

- · Low-jitter, high-accuracy outputs

- Up to three clock outputs

- Programmable output drive strength

- · Glitch-free outputs while frequency switching

- $\bullet$  Four independent output voltages: 3.3V, 3.0V, 2.5V, and 1.8V

- 8-pin SOIC package

- Commercial and Industrial temperature range

### Benefits

- Multiple high-performance PLLs allow synthesis of unrelated frequencies

- Nonvolatile programming for customized PLL frequencies, spread spectrum characteristics, drive strength, crystal load capacitance, and output frequencies

- Two Spread Spectrum capable PLLs with Lexmark profile for maximum for EMI reduction

- Spread Spectrum PLLs can be disabled or enabled separately

- PLLs can be programmed for system frequency margin tests

- Meets critical timing requirements in complex system designs

- · Suitable for PC, consumer, and networking applications

- · Ability to synthesize standard frequencies with ease

- Application compatibility in standard and low-power systems

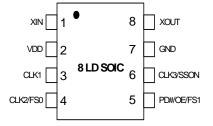

#### **Pin Configuration**

#### Pin Description - Memory Programmable 2-PLL device with 2 Spread Spectrum PLLs

| Pin Number | Name       | I/O          | Description                       |

|------------|------------|--------------|-----------------------------------|

| 1          | XIN        | Input        | Crystal or Clock Input            |

| 2          | VDD        | Power        | Power Supply                      |

| 3          | CLK1       | Output       | Programmable Clock Output         |

| 4          | CLK2/FS0   | Output/input | Programmable Clock Output or FS0  |

| 5          | PD#/OE/FS1 | Input        | Power Down, Output Enable or FS1  |

| 6          | CLK3/SSON  | Output/Input | Programmable Clock Output or SSON |

| 7          | GND        | Power        | Power Supply Ground               |

| 8          | XOUT       | Output       | Crystal Output                    |

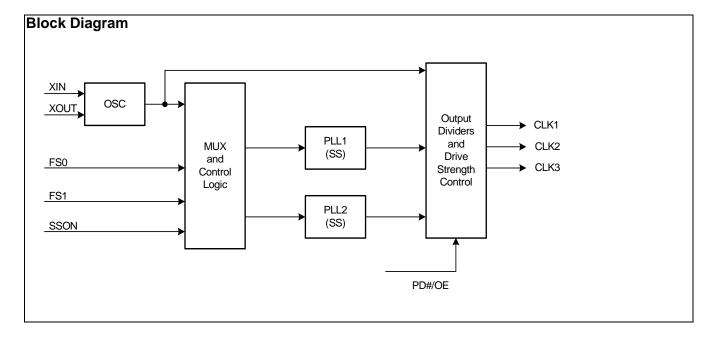

#### **General Description**

The CY25402 and CY25422 are two PLL programmable Spread Spectrum Clock Generators used to reduce EMI found in high-speed digital electronic systems. Both PLLs have Spread Spectrum capability. The spread spectrum feature are turned on or off using the control pin SSON.

The advantage of having two PLLs is that a single device can generate up to two independent frequencies from a single crystal or reference input frequency. Generally, a design requires up to two oscillators to achieve the same result with a single CY25402 or CY25422.

The device uses Cypress proprietary PLL and Spread Spectrum Clock (SSC) technology to synthesize and modulate the frequency of the input clock. By frequency modulating the clock, the measured EMI at the fundamental and harmonic frequencies are greatly reduced. This reduction in radiated energy significantly reduces the cost of complying with regulatory agency (EMC) requirements and improves time-to-market without degrading the system performance.

The CY25402 and CY25422 use a factory/field-programmable configuration memory array to provide customization for output frequencies, frequency select options, spread characteristics like spread percentage and modulation frequency, output drive strength and crystal load capacitance. A customized device are configured using Cyberclocks<sub>TM</sub> software or by contacting the factory.

The spread percentage is programmed to either center spread or down spread with various spread percentages. The range

for center spread is from  $\pm 0.125\%$  to  $\pm 2.50\%$ . The range for down spread is from -0.25% to -5.0%. Contact the factory for smaller or larger spread percentage amounts, if required.

The input to the CY25402 and CY25422 is either a crystal or a clock signal. The input frequency range for crystals is 8 MHz to 48 MHz, and for clock signals is 8 MHz to 166 MHz.

The CY25402 and CY25422 have up to three clock outputs and each output has three possible input sources. There are two frequency select lines FS(1:0) that provide an option to select four different sets of frequencies among the two PLLs. Each output has programmable output divider options. Output 1 has eight possible divider values and outputs 2–3 have four possible divider values for maximum flexibility. The 2 bit or 3 bit output dividers are programmable providing a wide output frequency range.

The outputs are glitch-free when frequency is switched using output dividers. The outputs have a predictable phase relationship if the clock source is the same PLL and divider values are 2, 3, 4, or 6.

The CY25402 and CY25422 are available in an 8-pin SOIC package with commercial and industrial operating temperature ranges.

#### Table 1. Supply Voltage Options

| Device  | V <sub>DD</sub> Supply Voltage |

|---------|--------------------------------|

| CY25402 | 2.5V, 3.0V or 3.3V             |

| CY25422 | 1.8V                           |

### **Absolute Maximum Conditions**

| Parameter          | Description                          | Condition                              | Min. | Max.           | Unit  |

|--------------------|--------------------------------------|----------------------------------------|------|----------------|-------|

| V <sub>DD</sub>    | Supply Voltage                       |                                        | -0.5 | 4.5            | V     |

| V <sub>IN</sub>    | Input Voltage                        | It Voltage Relative to V <sub>SS</sub> |      | $V_{DD} + 0.5$ | VDC   |

| Τ <sub>S</sub>     | Temperature, Storage                 | Non Functional                         | -65  | +150           | °C    |

| ESD <sub>HBM</sub> | ESD Protection (Human<br>Body Model) | MIL-STD-883, Method 3015               |      | -              | Volts |

| UL-94              | Flammability Rating                  | bility Rating @1/8 in.                 |      | -0             |       |

| MSL                | Moisture Sensitivity Level           | OIC package                            |      |                |       |

# **Recommended Operating Conditions**

| Parameter         | Description                                                                                                               | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>DD1</sub>  | Operating Voltage, 3.3V                                                                                                   | 3.0  | -    | 3.6  | V    |

| V <sub>DD2</sub>  | Operating Voltage, 3.0V                                                                                                   | 2.7  | -    | 3.3  | V    |

| V <sub>DD3</sub>  | Operating Voltage, 2.5V                                                                                                   | 2.25 | -    | 2.75 | V    |

| V <sub>DD4</sub>  | Operating Voltage, 1.8V                                                                                                   | 1.65 | -    | 1.95 | V    |

| T <sub>AC</sub>   | Commercial Ambient Temperature                                                                                            | 0    | -    | +70  | °C   |

| T <sub>AI</sub>   | Industrial Ambient Temperature                                                                                            | -40  | -    | +85  | °C   |

| C <sub>LOAD</sub> | Max. Load Capacitance                                                                                                     | -    | -    | 15   | pF   |

| t <sub>PU</sub>   | Power-up time for all $V_{\mbox{\scriptsize DD}}$ pins to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | -    | 500  | ms   |

### **DC Electrical Specifications**

| Parameter                      | Description                                | Conditions                                                               | Min.                  | Тур. | Max.                  | Unit |

|--------------------------------|--------------------------------------------|--------------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| V <sub>OL</sub>                | Output Low Voltage, All CLK pins           | All V <sub>DD</sub> levels, I <sub>OL</sub> = 8 mA                       | 0                     | _    | 0.4                   | V    |

| V <sub>OH</sub>                | Output High Voltage, All CLK pins          | All V <sub>DD</sub> levels, I <sub>OH</sub> = –8 mA                      | $V_{DD} - 0.4$        | -    | V <sub>DD</sub>       | V    |

| V <sub>IL</sub>                | All Inputs except XIN                      | All V <sub>DD</sub> levels                                               | -0.3                  | _    | 0.2 * V <sub>DD</sub> | V    |

| V <sub>IH</sub>                | All Inputs except XIN                      | All V <sub>DD</sub> levels                                               | 0.8 * V <sub>DD</sub> | -    | $V_{DD} + 0.3$        | V    |

| V <sub>ILX</sub>               | Input Low Voltage, clock input to XIN pin  | All V <sub>DD</sub> levels                                               | -0.3                  | -    | 0.36                  | V    |

| V <sub>IHX</sub>               | Input High Voltage, clock input to XIN pin | All V <sub>DD</sub> levels                                               | 1.44                  | -    | 2.0                   | V    |

| I <sub>ILPDOE</sub>            | Input Low Current, PD#/OE and FS0,1 pins   | V <sub>IN</sub> = V <sub>SS</sub><br>(Internal pull up = 100k typical)   | -                     | -    | 10                    | μA   |

| I <sub>IHPDOE</sub>            | Input High Current, PD#/OE and FS0,1 pins  | V <sub>IN</sub> = V <sub>DD</sub><br>(Internal pull up = 100k typical)   | -                     | _    | 1                     | μΑ   |

| I <sub>ILSR</sub>              | Input Low Current, SSON pin                | V <sub>IN</sub> = V <sub>SS</sub><br>(Internal pull down = 100k typical) | -                     | _    | 1                     | μA   |

| I <sub>IHSR</sub>              | Input High Current, SSON pin               | V <sub>IN</sub> = V <sub>DD</sub><br>(Internal pull down = 100k typical) | -                     | -    | 10                    | μA   |

| I <sub>DD</sub> <sup>[1]</sup> | Supply Current                             | All clocks running, CL = 0                                               | -                     | _    | 12                    | mA   |

| C <sub>IN</sub>                | Input Capacitance - All inputs except XIN  | SSON, OE, PD# or FS inputs                                               | -                     | _    | 7                     | pF   |

### **AC Electrical Specifications**

| Parameter                 | Description                                 | Conditions                                                            | Min. | Тур. | Max. | Unit |

|---------------------------|---------------------------------------------|-----------------------------------------------------------------------|------|------|------|------|

| F <sub>IN</sub> (crystal) | Crystal Frequency                           |                                                                       | 8    | -    | 48   | MHz  |

| F <sub>IN</sub> (clock)   | Input Clock Frequency (XIN)                 |                                                                       | 8    | -    | 166  | MHz  |

| F <sub>OUT</sub>          | Output Clock Frequency                      |                                                                       | 3    | -    | 166  | MHz  |

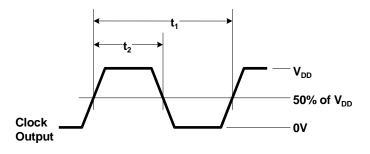

| DC                        | Output Duty Cycle All Clocks except Ref Out | Duty Cycle is defined in Figure 2; $t_1/t_2$ , 50% of V <sub>DD</sub> | 45   | 50   | 55   | %    |

| DC                        | Ref Out Duty Cycle                          | Ref In Min 45%, Max 55%                                               | 40   |      | 60   | %    |

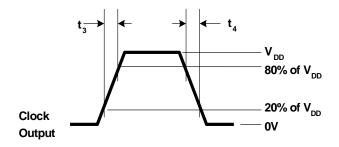

| E <sub>R</sub>            | CLK1-3 Rising Edge Rate                     | $V_{DD}$ = All, 20% to 80% $V_{DD}$                                   | 0.8  | -    | -    | V/ns |

| E <sub>F</sub>            | CLK1-3 Falling Edge Rate                    | $V_{DD}$ = All, 20% to 80% $V_{DD}$                                   | 0.8  | -    | -    | V/ns |

| T <sub>CCJ1</sub>         | Cycle-to-cycle Jitter                       | Configuration dependent. See Table 2                                  | -    | -    | -    | ps   |

| T <sub>LTJ</sub>          | Long Term Jitter                            | Configuration dependent. See Table 2                                  | _    | -    | -    | ns   |

| T <sub>10</sub>           | PLL Lock Time                               |                                                                       | -    | -    | 3    | ms   |

### Table 2. Configuration Example for Jitter

| Reference | Description       | Max Jitter (ps) on<br>Output 1(48MHz) | Max Jitter (ps) on Output 2<br>(27 MHz) | Max Jitter (ps) on<br>Output 3 (166 MHz) |

|-----------|-------------------|---------------------------------------|-----------------------------------------|------------------------------------------|

| 27MHz     | T <sub>CCJ1</sub> | 155                                   | 255                                     | 170                                      |

| 27MHz     | T <sub>LTJ</sub>  | 770                                   | 580                                     | 630                                      |

| 48 MHz    | T <sub>CCJ1</sub> | 135                                   | 225                                     | 100                                      |

| 48 MHz    | T <sub>LTJ</sub>  | 535                                   | 575                                     | 520                                      |

# **Recommended Crystal Specification for SMD Package**

| Parameter | Description                       | Range 1 | Range 2 | Range 3 | Unit |

|-----------|-----------------------------------|---------|---------|---------|------|

| Fmin      | Minimum Frequency                 | 8       | 14      | 28      | MHz  |

| Fmax      | Maximum Frequency                 | 14      | 28      | 48      | MHz  |

| R1(max)   | Maximum Motional Resistance (ESR) | 135     | 50      | 30      | Ω    |

| C0(max)   | Maximum Shunt Capacitance         | 4       | 4       | 2       | pF   |

| CL(max)   | Maximum Parallel Load Capacitance | 18      | 14      | 12      | pF   |

| DL(max)   | Maximum Crystal Drive Level       | 300     | 300     | 300     | μW   |

### **Recommended Crystal Specification for Thru-Hole Package**

| Parameter | Description                       | Range 1 | Range 2 | Range 3 | Unit |

|-----------|-----------------------------------|---------|---------|---------|------|

| Fmin      | Minimum Frequency                 | 8       | 14      | 24      | MHz  |

| Fmax      | Maximum Frequency                 | 14      | 24      | 32      | MHz  |

| R1(max)   | Maximum Motional Resistance (ESR) | 90      | 50      | 30      | Ω    |

| C0(max)   | Maximum Shunt Capacitance         | 7       | 7       | 7       | pF   |

| CL(max)   | Maximum Parallel Load Capacitance | 18      | 12      | 12      | pF   |

| DL(max)   | Maximum Crystal Drive Level       | 1000    | 1000    | 1000    | μW   |

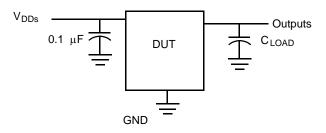

#### **Test and Measurement Setup**

#### Figure 1. Test and Measurement Setup

### **Voltage and Timing Definitions**

Figure 3. ER = (0.6 x V<sub>DD</sub>) /t<sub>3</sub>, EF = (0.6 x V<sub>DD</sub>) /t<sub>4</sub>

### **Ordering Information**

| Part Number <sup>[2]</sup> | Туре                      | VDD(V)          | Temperature Range          |

|----------------------------|---------------------------|-----------------|----------------------------|

| Lead-free                  |                           |                 |                            |

| CY25402SXC-xxx             | CY25402SXC-xxx 8-pin SOIC |                 | Commercial, 0°C to 70°C    |

| CY25402SXC-xxxT            | 8-pin SOIC-Tape & Reel    | 3.3, 3.0 or 2.5 | Commercial, 0°C to 70°C    |

| CY25402FSXC                | 8-pin SOIC                | 3.3, 3.0 or 2.5 | Commercial, 0°C to 70°C    |

| CY25402FSXC                | 8-pin SOIC-Tape & Reel    | 3.3, 3.0 or 2.5 | Commercial, 0°C to 70°C    |

| CY25422SXC-xxx             | 8-pin SOIC                | 1.8             | Commercial, 0°C to 70°C    |

| CY25422SXC-xxxT            | 8-pin SOIC-Tape & Reel    | 1.8             | Commercial, 0°C to 70°C    |

| CY25422FSXC                | 8-pin SOIC                | 1.8             | Commercial, 0°C to 70°C    |

| CY25422FSXCT               | 8-pin SOIC-Tape & Reel    | 1.8             | Commercial, 0°C to 70°C    |

| CY25402SXI-xxx             | 8-pin SOIC                | 3.3, 3.0 or 2.5 | Industrial, -40°C to +85°C |

| CY25402SXI-xxxT            | 8-pin SOIC-Tape & Reel    | 3.3, 3.0 or 2.5 | Industrial, -40°C to +85°C |

| CY25402FSXI                | 8-pin SOIC                | 3.3, 3.0 or 2.5 | Industrial, -40°C to +85°C |

| CY25402FSXIT               | 8-pin SOIC-Tape & Reel    | 3.3, 3.0 or 2.5 | Industrial, -40°C to +85°C |

| CY25422SXI-xxx             | 8-pin SOIC                | 1.8             | Industrial, -40°C to +85°C |

| CY25422SXI-xxxT            | 8-pin SOIC-Tape & Reel    | 1.8             | Industrial, -40°C to +85°C |

| CY25422FSXI                | 8-pin SOIC                | 1.8             | Industrial, -40°C to +85°C |

| CY25422FSXIT               | 8-pin SOIC-Tape & Reel    | 1.8             | Industrial, -40°C to +85°C |

Note

xxx Indicates Factory Programmable are factory programmed configurations. For more details, contact your local Cypress FAE or Cypress Sales Representative.

F in the part number indicates field programmable using CyberClocks Online software.

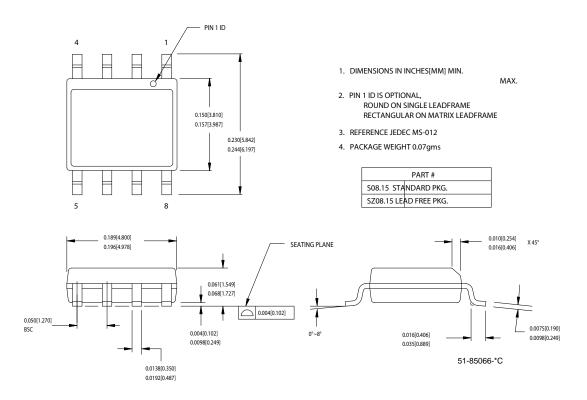

#### **Package Drawing and Dimensions**

#### Figure 4. 8-lead (150-Mil) SOIC S8

All products and company names mentioned in this document may be the trademarks of their respective holders.

© Cypress Semiconductor Corporation, 2006. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

# **Document History Page**

| Document Title: CY25402/CY25422 Two PLL Programmable Clock Generator<br>with Spread Spectrum<br>Document Number: 001-12565 |                                         |         |     |                              |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------|-----|------------------------------|

| REV.                                                                                                                       | REV. ECN NO. Issue Orig. of Date Change |         |     | Description of Change        |

| **                                                                                                                         | 690296                                  | See ECN | RGL | New Data Sheet               |

| *A                                                                                                                         | 815788                                  | See ECN | RGL | Minor Change: To post on web |